## Use with the Following Devices

M88, M68, M64, Si5118, Si5332, Si5334, Si5335, Si5338, Si5340, Si5341, Si5342, Si5342H, Si5344H, Si5344H, Si5345, Si5346, Si5347, Si5348, Si5350, Si5351, Si5355, Si5356, Si5357, Si5360, Si5361, Si5362, Si5363, Si5371, Si5372, Si5380, Si5381, Si5382, Si5383, Si5384, Si5386, Si5388, Si5389, Si5391, Si5392, Si5394, Si5395, Si5396, Si5397, Si5401, Si5402, Si5403, Si5508, Si5510, Si5512, Si5518, Si51210, Si51211, Si51214, Si51218, Si53352, Si53354, Si53358, SKY63101, SKY63101, SKY63102, SKY63103

## Use with the Following EVBs

| M88/M68/M64     | M-EVK                                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------------------------|

| Si5332          | Si5332-12EX-EVB, Si5332-8EX-EVB, Si5332-6EX-EVB, Si5332-12IX-EVB, Si5332-8IX-EVB, Si5332-6IX-EVB,         |

|                 | Si5332-8A-EVB (Si5332-AM2-QFN40-EVB), Si5332-6A-EVB (Si5332-AM1-QFN32-EVB), Si5332-12A-EVB (Si5332-       |

|                 | AM3-QFN48-EVB)                                                                                            |

| Si5338          | Si5338-EVB                                                                                                |

| Si534x/7x/8x/9x | Si5340-D-EVB, Si5340-EVB, Si5341-D-EVB, Si5341-EVB, Si5342-D-EVB, Si5342-EVB, Si5344-D-EVB, Si5344-EVB,   |

|                 | Si5344H-EVB, Si5345-D-EVB, Si5345-EVB, Si5346-D-EVB, Si5346-EVB, Si5347-D-EVB, Si5347-EVB,Si5348-D-EVB,   |

|                 | Si5348-E-EVB, Si5348-EVB, Si5372A-A-EVB, Si5372J-A-EVBs, Si5380A-D-EVB, Si5380-D-EVB, Si5381A-E-EVB,      |

|                 | Si5381-EVB, Si5382A-E-EVB, Si5382-EVB, Si5383-D-EVB, Si5386A-E-EVB, Si5389-EVB, Si5389F-EVB, Si5391A-A-   |

|                 | EVB, Si5391P-A-EVB, Si5392E-A-EVB, Si5394A-A-EVB, Si5394E-A-EVB, Si5394P-A-EVB, Si5395A-A-EVB, Si5395E-A- |

|                 | EVB, Si5395P-A-EVB, Si5397A-A-EVB                                                                         |

| Si535x          | Si535X-B20QFN-EVB, Si5356-EVB, Si5357-EVB                                                                 |

| Si536x          | Si5360-A-EVB, Si5361-A-EVB, Si5362-A-EVB, Si5363-A-EVB                                                    |

| Si540x          | Si540x-A-EVB                                                                                              |

| Si55xx          | Si55xx-A-EVB                                                                                              |

| SKY6310x        | SKY63101AA-EVB, SKY63102AA-EVB, SKY63103AA-EVB                                                            |

| Si51211x        | Si51211-EVB, Si51218-EVB                                                                                  |

|                 |                                                                                                           |

## **PC System Requirements**

Operating System:

ClockBuilder Pro (CBPro) requires Windows 7 Service Pack 1, Windows 8.1 Update, Windows 10 v1607-v1809, or Windows 11. Either 32- and 64-bit versions are supported.

CBPro uses Microsoft.NET Framework version 4.8. The installer will check to see if it is installed and, if not, prompt to automatically download and install it. Newer Windows operating systems will already have .NET 4.8 installed.

If you need to install CBPro on a PC that does not have an Internet connection and does not have .NET 4.8, you can download Microsoft's stand-alone installer from <u>https://go.microsoft.com/fwlink/?linkid=2088631</u>. Install .NET 4.8 before running the CBPro installer.

1024 x 768 screen resolution or greater

USB 2.0 or higher if you want to connect to a supported EVB

## **Export Regulations**

The International Traffic in Arms Regulations (ITAR), 22 C.F.R. sections 120-130, governs the export and re-export of defense articles, defense services and related technical data from the United States to any foreign destination, or to any foreign person, whether located in the United States or abroad. ClockBuilderPro is not authorized to create Orderable Part Numbers (OPNs) for use with products that are subject to export control regulations under ITAR. Do not use this software to create an OPN if you do not have a license from the U.S. Department of State's Directorate of Defense Trade Controls (DDTC) to export the configuration files outside of the United States.

Note: alternatives to OPNs include in-system programming of device configuration and burning non-volatile memory using ITAR compliant processes. Please review ClockBuilder Pro Tools & Support for In-System Programming documented bundled with CBPro

for additional information. Contact your local Skyworks sales office or distributor for assistance or email us at <u>sales@skyworksinc.com</u>.

| Firmware<br>Version | Release Notes         | First Support In                 | Last Supported In                                                                                                                               |

|---------------------|-----------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0                 | N/A (initial release) | <u>CBPro 4.2</u> [ 2022-01-31 ]  | N/A (still supported by CBPro, but not recommended<br>for new or updated designs; see <u>Si5512/18 PTP-</u><br><u>Steered RF + SyncE Mode</u> ) |

| 1.1                 | Release Notes         | <u>CBPro 4.5</u> [ 2022-08-23 ]  | N/A (still supported)                                                                                                                           |

| 1.2                 | Release Notes         | <u>CBPro 4.10</u> [ 2023-07-31 ] | N/A (still supported)                                                                                                                           |

| 1.3                 | Release Notes         | <u>CBPro 4.13</u> [ 2024-05-31 ] | N/A (still supported)                                                                                                                           |

| 1.4                 | Release Notes         | <u>CBPro 4.14</u> [ 2024-12-2 ]  | N/A (still supported)                                                                                                                           |

| 1.5                 | Release Notes         | <u>CBPro 4.15</u> [ 2025-04-18 ] | N/A (still supported)                                                                                                                           |

# Si536x/Si540x/55xx Firmware Release Notes & CBPro Support Matrix

# Si536x/Si540x/Si55xx CBPro, Planner, and Firmware Version Correlation Table

|                  | Software and Fi                           | rmware Versionin                                                                                    | g                   | Hardware Support |        |        |                      |  |

|------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------|------------------|--------|--------|----------------------|--|

| CBPro<br>Version | CBPro Planner<br>Version <sup>1,3,5</sup> | Si55xx/Si540x<br>FW Version <sup>2,4,5</sup>                                                        | CBPro<br>Build Date | Si55xx           | Si540x | Si536x | Notes                |  |

| <u>4.15.0.3</u>  | 25.4.10.914<br>or<br>1.0.0.7371           | 1.5.0.17393 or<br>1.4.0.16122 or<br>1.3.0.14049 or<br>1.2.0.11252 or<br>1.1.0.8413 or<br>1.0.0.6566 | 2025-05-21          | Y                | Y      | Y      | Firmware 1.5 release |  |

| <u>4.14</u>      | 24.11.22.773<br>or<br>1.0.0.7371          | 1.4.0.16122 or<br>1.3.0.14049 or<br>1.2.0.11252 or<br>1.1.0.8413 or<br>1.0.0.6566                   | 2024-12-2           | Y                | Y      | Y      | Firmware 1.4 release |  |

| <u>4.13.0.3</u>  | 24.5.30.588 or<br>1.0.0.7371              | 1.3.0.14049 or<br>1.2.0.11252 or<br>1.1.0.8413 or<br>1.0.0.6566                                     | 2024-08-06          | Y                | Y      | Y      | Firmware 1.3 release |  |

| <u>4.12.0.3</u>  | 24.1.17.436 or<br>1.0.0.7371              | 1.2.0.11252 or<br>1.1.0.8413 or<br>1.0.0.6566                                                       | 2024-03-06          | Y                | Y      | Y      |                      |  |

| <u>4.11.0.1</u>  | 23.8.17.336 or<br>1.0.0.7371              | 1.2.0.11252 or<br>1.1.0.8413 or<br>1.0.0.6566                                                       | 2023-09-14          | Y                | Y      | Y      | Si5360 launch        |  |

| <u>4.10</u>      | 23.7.10.271 or<br>1.0.0.7371              | 1.2.0.11252 or<br>1.1.0.8413 or<br>1.0.0.6566                                                       | 2023-07-31          | Y                | Y      | Y      | Firmware 1.2 release |  |

| <u>4.9</u>       | 1.1.5.10066 or<br>1.0.0.7371              | 1.1.0.8413 or<br>1.0.0.6566                                                                         | 2023-04-11          | Y                | Y      | Y      |                      |  |

| <u>4.8</u>       | 1.1.3.9396 or<br>1.0.0.7371               | 1.1.0.8413 or<br>1.0.0.6566                                                                         | 2023-02-14          | Y                | Y      | Y      |                      |  |

| <u>4.7</u>       | 1.1.0.9153 or<br>1.0.0.7371               | 1.1.0.8413 or<br>1.0.0.6566                                                                         | 2022-11-18          | Y                | Y      | Y      | Si5361/2/3 launch    |  |

| <u>4.6</u> | 1.1.0.8801 or<br>1.0.0.7371 | 1.1.0.8413 or<br>1.0.0.6566 | 2022-10-07 | Y | Y | N | Si5512/18 PTP-Steered RF + SyncE<br>projects should update to this CBPro<br>release and firmware 1.1.0                                                                    |

|------------|-----------------------------|-----------------------------|------------|---|---|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>4.5</u> | 1.1.0.8448 or<br>1.0.0.7371 | 1.1.0.8413 or<br>1.0.0.6566 | 2022-08-23 | Y | Y | N | CBPro 4.5 drops support of pre-<br>production engineering sample ICs                                                                                                      |

| <u>4.4</u> | 1.0.0.6567                  | 1.0.0.6566                  | 2022-03-30 | Y | Y | N |                                                                                                                                                                           |

| <u>4.3</u> | 1.0.0.6567                  | 1.0.0.6566                  | 2022-02-23 | Y | Y | N |                                                                                                                                                                           |

| <u>4.2</u> | 1.0.0.6567                  | 1.0.0.6566                  | 2022-01-31 | Y | Y | N |                                                                                                                                                                           |

| <u>4.1</u> | 0.10.1.5353                 | 0.10.1.5352                 | 2021-09-22 | Y | Ν | N | Last version where PPS PLL is small<br>enough to fit into NVM. Plans using<br>PPS PLL with CBPro > 4.1 must load<br>PPS_PLL plans via the HOST_LOAD<br>command post-boot. |

| <u>4.0</u> | 0.10.1.5200                 | 0.10.1.5196                 | 2021-07-26 | Y | Ν | N |                                                                                                                                                                           |

| Pre-4.0    | Varies                      | Varies                      | Varies     | Ν | Ν | N | ClockBuilder Pro <4.0 is no longer<br>supported for Si55xx/Si540x. Upgrade<br>to the latest version when possible.                                                        |

## SKY63101/2/3 Firmware Release Notes & CBPro Support Matrix

| Firmware<br>Version | Release Notes         | First Support In                 | Last Supported In     |  |  |  |

|---------------------|-----------------------|----------------------------------|-----------------------|--|--|--|

| 1.0                 | N/A (initial release) | <u>CBPro 4.15</u> [ 2025-04-18 ] | N/A (still supported) |  |  |  |

## SKY63101/2/3 CBPro, Planner, and Firmware Version Correlation Table

|                  | Software and Fi                           | rmware Versioning                       | 5                   |              | Hardware Support     |

|------------------|-------------------------------------------|-----------------------------------------|---------------------|--------------|----------------------|

| CBPro<br>Version | CBPro Planner<br>Version <sup>1,3,5</sup> | SKY6310x FW<br>Version <sup>2,4,5</sup> | CBPro<br>Build Date | SKY63101/2/3 | Notes                |

| <u>4.15.0.3</u>  | 25.4.10.914                               | 1.5.0.17393                             | 2025-05-21          | Y            | Firmware 1.0 release |

Footnotes for tables above:

- 1. The CBPro Planner is the algorithmic engine (embedded in CBPro) that generates programming data based on project configuration.

- 2. Firmware version is the version of firmware that runs on the MCU within the clock device. The firmware processes Device API command requests and manages the clock device's registers during operation. The firmware is included along with the user configuration when exporting for in-system programming or creating an Orderable Part Number (OPN, where supported).

- 3. Each planner/FW version is tied to a specific ClockBuilder Pro version. To roll back to a pre-release firmware version, use an earlier ClockBuilder Pro version. Contact Skyworks for support when necessary.

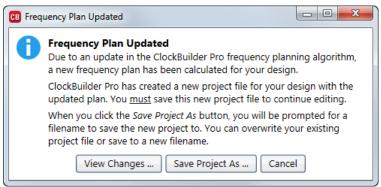

- 4. To upgrade the user frequency configuration to a new cbpro version, see the PowerPoint titled "ClockBuilder Pro Version Upgrade Instructions", linked to in the documentation panel within ClockBuilder Pro

- 5. When multiple planner and firmware versions are listed, which version to use is user selectable. Only firmware version is selected: the associated planner version is automatically used and documented in the project's design report.

## **CBPro Revision List**

CBPro releases are documented in reverse chronological order in the sections that follow. See *CBPro Revision Index* at the end of this document for a linked list of all official CBPro releases.

# CBPro v4.16 [ 2025-06-25 ]

Added support for **SKY63104/5/6** 12-Output, Any-Frequency, Any-Output Jitter Attenuators/Clock Multipliers with Ultra-Low Jitter.

Added support for **SKY62101** 12-Output, Any-Frequency, Any-Output Clock Generator.

Miscellaneous

- The phase noise request wizard now has an option to create an additive jitter report. (TMGSW-4057)

- ✓ Include buffer additive jitter measurements

| Si53302 | ▾ |

|---------|---|

|---------|---|

### Si536x/55xx/540x, SKY6xxxx

- Fixed: if a project had previously configured a GPIO on a pin that was later forced to a fixed function like external flash SIF, the old function was reported in the design report and could generate a DRC error about the old state (programming data would not have had an issue). (TMGSW-4277)

- Fixed: FOTF with firmware 1.5 would generate an error.

- Fixed: multi-profile (MP) 'master' project editor bugs: (TMGSW-4286)

- If a non-MP project was opened and OUTx were enabled or OUTx pins were used for GPIO, when the project was converted to MP the OUTx GPIO(s) were not available for assignment as FPLAN SELx pin.

- If a MP project serial interface mode was changed, the available FPLAN\_SELx pins were not adjusted.

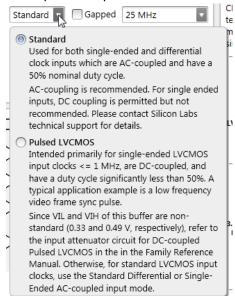

- Added gapped clock support through new 'Clock Type' column on the Inputs page: (TMGSW-4335)

- This replaces the Holdover Reference column. Gapped clock is not available if the clock is assigned to a modulated PLL. It is also not allowed if the Frequency is not in the range 7.5M to 1 GHz.

- Gapped clock is available on Glock Generators.

- The holdover reference type on Si55xx Netsync wireless can no longer be defined. The clock type is simply fixed at OCXO/TCXO for PLLR inputs on dual reference topologies.

- PHMON is disabled.

- LOS is force enabled and auto set mode is force enabled with special settings for gapped clock input.

- There are new DRC checks in gapped clock mode, and every input that is gapped will have an associated info DRC.

- Frequency plan burn files (user\_config.burn) now embed information such that the burn will be aborted if the device part number does not match project part number. (TMGSW-4233)

- CBProPatchBurnfileExport CLI is now available to create NVM patch files from the command line. (TMGSW-3394)

- SKY69001/2, SKY63101/2/3, SKY69101 Integrated BAW:

- Improve various topology labels. (TMGSW-4360)

- Add support for Frequency-on-the-Fly using the CBProFOTF3 command line tool. (TMGSW-4229)

- Tighten OOF Clear and Set Thresholds: (TMGSW-4169)

- Was: Clear: 0.1 to 500 ppm, Set: Clear to 500 ppm.

- Now: Clear: 1.0 to 500 ppm, Set: Clear + 0.02 to 500 ppm.

- Add warning to NVM program tool for VDDA supply voltage in low power mode. (TMGSW-3385)

- Design ID is no longer prompted for in the OPN wizard for a blank part OPNs or multi-profile projects. In blank part mode, there is no user\_config and therefore APP\_INFO will not be available or report empty. For multi-profile projects, the "master" project does not have a Design ID. Each profile has one and these are configured independently and stored in flash. (TMGSW-4288)

- Add support for exporting a special boot file that will clear FWERR and HWERR in READ\_REPLY STATUS byte. Created one of two ways: (TMGSW-4321; COGSFW-5170)

- Checking a new option on the Bootfile export tool

- Save additional files

- Save FWERR and HWERR clear bootfile 🔋 <

- Save design report

- Passing new --create-clear-errs-file argument to CBProBootFileExport CLI

The HWERR or FWERR bits, which are sticky and cannot be cleared with existing API commands, will be cleared when this file is loaded into the device using the HOST\_LOAD command. This can be useful in situations like setting up a device to boot from an external flash that is either unconnected or blank.

- When writing to a DUT volatily and Device API checks show an issue such as REFERENCE\_STATUS INVALID, the message shown is now a warning and explains that the plan was written without error. (TMGSW-2870)

- Update PLL configure page help for clarity. (TMGSW-4353)

#### Si534x/8x

• Fixed broken link for AN905. (TMGSW-4295)

## CBPro v4.15.0.3 [ 2025-05-21 ]

Fixed: output static skew was disabled on SKY63101/2/3. (TMGSW-4302)

## CBPro v4.15.0.2 [ 2025-05-07 ]

Fixed: phase noise report requests inadvertently tagged requests in Salesforce with "TEST...IGNORE."

## CBPro v4.15.0.1 [ 2025-04-21 ]

SKY63101/2/3: fixed: creating a new project would raise an error. (TMGSW-4269)

## CBPro v4.15 [ 2025-04-18 ]

Jump To: <u>CBPro</u> - <u>AccuTime Assistant</u> - <u>Si536x/540x/55xx Firmware 1.5</u>

### **CBPro Release Notes**

Added support for SKY63101/2/3 16-Output, Jitter Attenuators/Clock Multipliers with Integrated Reference. These JAs combine sixth-generation DSPLL<sup>®</sup> and MultiSynth<sup>™</sup> technologies with an integrated Skyworks Bulk Acoustic Wave (BAW) oscillator to deliver ultra-low jitter (<45 fs) for high-performance applications like 112G and 224G SerDes and Coherent Optics.

Miscellaneous

- Phase noise requests now create a Salesforce case. The wizard has a few changes to reflect the update, and the submitter must now have a Salesforce account to create the request. (TMGSW-3799)

- Added option to CBProRegistersToSettings CLI to ignore unknown register addresses. This CLI converts register address, data pairs (dumps) into named setting breakout.

#### Si536x/55xx/540x

- Firmware 1.5 is now available and is the default for new projects. See <u>release notes</u> for more information.

- Fixed: in EVB GUI Device API tab, if APIERR was asserted in command REPLY but the command reply length was less than 3, the reported error code was not correct. (TMGSW-4232)

#### ClockBuilder Pro Release Notes

- Fixed: Si55xx: VCXO buffered outputs gave error if VCXO frequency was > 650 MHz. (TMGSW-4215)

- Si55xx: improve error message if HCSL mode VCXO buffered output would be > 500 MHz. (TMGSW-4215)

- Si5360: in low power mode, add DRC error if there are multiple input frequencies into INx or XTAL/XO. (TMGSW-3321)

- Si5360/1/2/3: enable phase noise request from the project dashboard page. (TMGSW-4159

- Si55xx/540x: support OPNs and NVM burn when PPS PLL is used and FW1.5 is selected. Frequency plan NVM patching is not supported, however, due to "compressed" frequency plan NVM storage. (TMGSW-4078)

- Force disable fastlock in more cases: PLLA in dual ref JA mode and PLLR in single ref PTP Steered-RF mode. (TMGSW-4022)

- Removed DRC error that would be raised if a sync group had a SYNC but no SYSCLK. (TMGSW-4019; TMGSW-4011)

- Updated project samples: added Si5401/2 samples and updated Si5512/18 small cell samples. (TMGSW-3631)

- Added DRC warning if an R divider is odd (other than bypassed R=1). Previously this triggered an error if the duty cycle was <= 49%. (TMGSW-4054)

- Changed how startup outputs are enabled to support OUTPUT\_ENABLE Device API working in conjunction with OE/OEb pin. (TMGSW-4129)

- Changed DRC "cannot have non-PPS SYNC clocks without at least 1 PPS SYNC" to apply only to group 0. (TMGSW-3685)

- Support configuring OE API/pin logic mode when firmware 1.5 is selected. If a project with earlier firmware is opened, has OE GPI configured, and selects newer firmware, you will be notified via alert dialog of the change. (TMGSW-4221)

- Made GPIO behavior -- sticky vs. live configurable with firmware 1.1+. Default is existing behavior, sticky. (TMGSW-4040)

### Si5332

• Fixed: for multi-profile projects, I2C address was not included in NVM export / OPN creation, resulting in default address 0x60 being used. This affects CBPro 4.12.9 and higher. (TMGSW-4226)

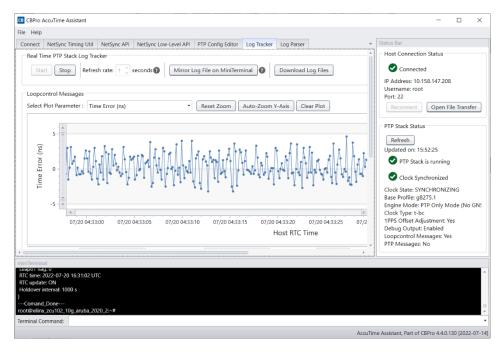

### AccuTime Assistant Release Notes

- Add ability to specify location of config files and their patterns.

- Add ability to specify ps command use to check for running processes.

- New support wizard! The wizard prompts for user/application information, collects debug information from the host and DUT, and creates a Salesforce ticket. The wizard also has a mode to collect debug information without creating a ticket. (TMGSW-4238)

### Si536x/540x/55xx Firmware 1.5 Release Notes

#### PPS PLL Notice

• The PPS PLL is designed to accommodate and filter reasonable levels of noise on its input signal. However, "runt" pulses can cause instability. To avoid this, such pulses should be squelched external to the Skyworks' device, for example by gating the 1PPS stream with a hardware or software-derived "1PPS valid" indicator.

#### Newly Added Features

- The PPS image can now fit in NVM for any new part number created using FW 1.5. (COGSFW-4933)

- The OUTPUT\_ENABLE API can now be used in conjunction with the the GPIO OE pins. The API command and GPIO will now either be logically OR'd or AND'd to enable the selected output. A new selection has been added to CBPro to choose the preferred logic. Existing plans will default to a logical OR functionality, which avoids compatibility issues with previous firmware versions where the GPIO and API were mutually exclusive. (COGSFW-4919)

**Bug Fixes**

- Fixed a bug where the PLL\_STATUS.LOOP\_FILTER\_RAMP\_IN\_PROGRESS API did not accurately report in all scenarios. (COGSFW-4978)

- Improved API stability for the PPS PLL in the event of an innerloop failure. (COGSFW-4940)

Additional Changes to Existing Features/Functionality

- To fit PPS into NVM, we had to disable the crystal oscillator calibration routine. To maintain compliance with datasheet phase noise spec, xtals can no longer be used with the PPS PLL for FW 1.5. If xtal and PPS PLL usage is required, please continue to use FW v1.4, where the PPS PLL can be HOST\_LOADED into the device. (COGSFW-4891)

- Now that OE can be controlled by both API and GPIO, the OUTPUT\_ENABLE API reply stream now shows the status of outputs both controlled by the API and by pins. (COGSFW-4923)

## CBPro v4.14 [ 2024-12-2 ]

Jump To: <u>CBPro</u> - <u>AccuTime Assistant</u> - <u>Si536x/540x/55xx Firmware 1.4</u>

### CBPro Release Notes

#### Miscellaneous

- Fixed: in the power estimation window, clicking the board/Theta-JA popup would crash CBPro. (TMGSW-3810)

- Fixed: EVB GUI DUT settings editor column labels might not be aligned with the setting rows. (TMGSW-3479)

- Fixed: CBPro could crash if the EVB GUI window was closed very near to EVB disconnect. (TMGSW-3751)

- Fixed: for register-based devices such as Si534x/7x/8x/9x and Si5332, the CBProDeviceWrite CLI with project file source and the field programmer target could generate a programming sequence that included read-only registers programmed in the OPN by PTE. This would have no effect in device programming result, but could be confusing if the registers were inspected and traced back to the reference manual. (TMGSW-3965)

- The phase noise request wizard now lists output names matching their names in the wizard in all cases, such as Si5357. (TMGSW-3006)

- The project converter now allows you to search by source and destination part numbers. (TMGSW-3912)

#### Si536x/55xx/540x

- Bug Fixes

- Fixed: for certain configurations, CBPro could crash if the Pulse Width Select page was selected. (TMGSW-3720)

- Fixed: INx\_LOS, INx\_OOF, and FAIL\_INx GPIOs were unavailable for configuration for new projects until the project was saved and re-opened. (TMGSW-3755)

- Si5360: fix possible "Specified method is not supported" error. (TMGSW-3729; TMGSW-3758)

- Fixed: JESD\_SYSREF\_PULSER and other commands were not appearing in EVB GUI in firmware 1.3 and 1.4. (TMGSW-3815; COGSFW-4570)

- Fixed: CBPro would crash if the EVB GUI Status API had been opened against FW1.1+ device or one with no firmware at all and then a FW1.0 project file was written. (TMGSW-3953)

- Fixed: in OPN blank part mode but including firmware, the firmware version selection was ignored and the latest (v1.4 for Si5500) was always assumed. (TMGSW-3951)

- Fixed: CBPro could show a notice about out-of-date firmware version when opening a project if the project was blank part w/out firmware.

- Fixed: if a ZDM output did not have a corresponding ZDM input, DRC system failed, and you could not save the project file. (TMGSW-3987)

- Fixed: the EVB GUI low level Device API command bytes display was too small to show full value. (TMGSW-3754)

- Si5500 firmware 1.4 is now available in the revision selector: (TMGSW-3827)

- This is the default for new projects. You will see a notice and DRC warning if a firmware 1.3 or earlier project is opened. See <u>release notes</u> below.

- A new boot and burn file will be included in exports, patch\_rom.boot and patch\_rom.burn, when firmware 1.4 is selected. This must be loaded if doing in-system programming. These files are automatically handled by various CBPro tools such as Write DUT, NVM Program Tool, Orderable Part Number (OPN) creation, and associated command line tools.

- Set PLLB bandwidth to 300 Hz in Single Reference PTP Steered-RF mode. (TMGSW-4020)

- The NVM burn program has been updated from v1.1 to v1.2.1. This new version provides enhanced error checking and supports pre-production parts. NVM export will include this new version. (TMGSW-3945)

- Si540x: added support for configurable dual reference mode on the Topology page: jitter attenuator (JA) or clock generator (CG) mode. Previously JA or CG mode was auto selected based on PLLA enable. Existing projects should select the previously used mode when opened. (TMGSW-3890)

- Si5361/2/3: added support for any OOF reference. There is a new DRC warning when INx is selected, as a high stability input, like a TCXO/OCXO, should be OOF reference to ensure higher accuracy OOF monitoring. When the selected OOF reference is not presented to the device, input clocks cannot be validated and will all show OOF alarms until this reference is provided. (TMGSW-3924)

- Si5361/2/3: improved the Info DRC if no output has been manually assigned to a Q divider. The DRC will now only be triggered if the final dividers are not all on a Q divider. This avoids triggering the DRC when all outputs can be auto assigned to Q and Nx remain unused. (TMGSW-3893)

- Added PLL\_STATUS FORCE\_HOLDOVER and PLL\_SHORT\_TERM\_HOLDOVER bits to the EVB GUI Status API tab. (TMGSW-3183)

- Updated the Qualcomm small cell reference Si5518 project samples and added Si5512 versions. (TMGAPPS-3431)

- It is now a DRC error if a GPIO is setup for a now unused input (was warning). (TMGSW-3755)

- Reflect the HCSL output max frequency limit in the frequency editor popup text in addition to the custom DRC error message. (TMGSW-3803).

- An error message will be shown if you try to write a firmware v1.3 PPS\_PLL project to the CEVB. This is not supported due to incompatibility of the existing DUT on the EVB. There is <u>no</u> issue with customer OPNs or host loading to a firmware v1.3 PPS\_PLL project to a customer DUT. (TMGSW-3868)

- On the Revision page, added an info tooltip next to the firmware version selector that explains configuration/firmware compatibility. (TMGSW-3894)

- When programming a DUT, added 5 msec delay after all RESTART command calls. Without this, it is possible for the serial interface to lock up and CTS never returns 1 (ready). (TMGSW-3789)

- If an output has 1 or 2 output driver GPOs, set the driver to Stop Hi-Z. (TMGSW-3783)

- The NVM Patching User's Guide link is now shown on the dashboard of all parts (TMGSW-3730)

- Improved DCO DRC rules and checks: (TMGSW-3812):

- DRC warning when when >=2 dividers are DCO Enabled with different actual DCO step size.

- DRC error when FINC/FDEC Enabled dividers are not all identical Actual Step Size values.

- Added support for Spread Spectrum (SSC) (TMGSW-3552)

- You must select firmware 1.4 on the "Device Revision & Grade" page and check SSC on "Device Feature Configuration" page.

- For Si540x devices, SSC is enabled on the Topology page. For other devices, SSC is enabled on the new Spread Spectrum page. This page must be enabled on the Device Feature Configuration page.

- $\circ$   $\,$  When SSC is enabled, a new SSEN SS enable GPI pin can be configured on the GPIO page.

- Si5361: removed the DRC check that required NA to be used before NB could be. This will now support NB SSC without NA. The device grade 'B' meaning was updated as a result: (TMGSW-3946)

- A: Both NA and NB used

- B: Only one of NA or NB used

- C: Neither NA or NB used

- H: High frequency grade

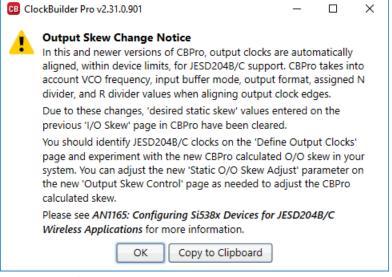

- New static skew calculator added to CBPro: (TMGSW-3363)

- Available when the "Output Skew Control" feature has been enabled on Step 1 of CBPro.

- $\circ$   $\;$  Launch via new button on the bottom of that page:

|   | Output Skew R        | eport     | Abo | ut Static Skew | Static      | Skew  | Calcu   | lator . |  |

|---|----------------------|-----------|-----|----------------|-------------|-------|---------|---------|--|

| 0 | Example:             |           |     |                |             |       |         |         |  |

|   | CB CPW Calculator    |           |     |                |             | _     |         | ×       |  |

|   | <b>G .</b>           |           |     |                |             |       |         |         |  |

|   | Dielectric Thickness | 0.000 🗧 n | nil |                | Skew Meter: | 2,358 | .654 pS | 5/m     |  |

|   | Track Width          | 0.000 🗘 n | nil | Calculate      | Skew Inch:  | 59.91 | 0 pS/in | 1       |  |

|   |                      |           |     |                | Z0:         | 133.2 | 86 Ω    |         |  |

|   | Gap Width            | 0.000 딎 n | nil | Сору           | Eeff:       | 0.500 |         |         |  |

|   | Er                   | 0.000     |     | Сору           | Vp:         | 1.414 |         |         |  |

|   |                      |           |     |                |             |       |         |         |  |

- EVB GUI: disable regulator controls during on/off toggle, voltage change, and power measurement to ensure the UI does not get out of sync with the EVB state. (TMGSW-3882)

- Added new "Device API Documentation" link to CBPro's welcome screen that explains how to generate and view Host API HTML documentation.

#### Si534x/7x/8x/9x

- Fixed: if DCO was enabled on a divider and then switched output to be Auto, DCO was not forced disabled until you visited the DCO page.

- Fixed: Si5386: if MB was DCOd, FRACNB\_EN was not forced to 1 when MB was integer (TMGSW-3837)

- Added a DRC error if an N divider is < 10 when DCO is enabled. (TMGSW-3721)

- Si5348: added a DCO warning to the free run page. (TMGSW-780)

- Stopped including OE0\_PIN\_MSK on design reports and register exports when only 1 OE pin, since it is always configured for all outputs. (TMGSW-3333)

- Si539x: added text to the dynamic skew tooltip regarding reset volatility. (TMGSW-1899)

#### Si512xx

• Fixed: CBPro crash when selecting the Pin&Clock page. (TMGSW-3834)

#### Si535x

• Improved frequency planner algorithm for non-spread spectrum configurations: choose integer Nx and M when possible; if not, select integer N solution if available before falling back to fractional Nx solution. (TMGSW-3316)

#### AccuTime Assistant Release Notes

- The "PTP Config Editor" tab is now available offline if the user connects at least once to a device running AccuTime.

- Fixed some spelling errors. (TMGSW-3900)

- Renamed 'PTP2 Info' tab to 'PTP Info' (TMGSW-3907).

- Renamed "Log Tracker" tab to "PTP Log Tracker" (TMGSW-3907).

- Implemented a more robust check for application running using "pidof" (TMGSW-3899).

- Added support for pre-release devices. (TMGSW-3776)

- Added warning for older AccuTime release host download incompatibility with A1 die revisions. (TMGSW-3776)

#### ClockBuilder Pro Release Notes

- Added support for AccuTime v4.0. (TMGSW-3813)

- Added ability to obsolete configuration parameters at a specific version of AccuTime. (TMGSW-3813)

- Added an indicator in the status bar to indicate whether the sync timing core driver is running or not. (TMGSW-3908).

- Allow User to specify SSH port for SSH Communication to AccuTime. (TMGSW-4023)

- The User Guide was updated.

### Si536x/540x/55xx Firmware 1.4 Release Notes

#### Newly Added Features

• Added spread spectrum support for select products. (COGSFW-4042)

#### Bug Fixes

- For previous firmware versions where an output was included in both Sync Group 0 and 1, users may have seen incorrect phase step sizes when executing the PHASE\_JAM\_SYNC\_OUT command. Now shared sync/pps outputs between groups now honor sysclk requirements for both groups. (COGSFW-4347)

- For frequency plan using OSYNCb, loading a new frequency plan will cause the part to lock up. A boot file has been created to disable OSYNCb in a frequency plan. This boot file should be sent before issuing the RESTART command. If you need to in-system program an OSYNC frequency plan with firmware 1.3, please contact Skyworks for assistance. (COGSFW-4618)

- Version 1.3 of the Si5500 firmware has a bug that causes dynamic phase adjust to not work properly. The bug has been fixed in firmware 1.4. (COGSFW-4823)

- An issue was discovered in firmware 1.3 with plans that use a crystal oscillator (XTAL). This has been fixed in firmware 1.4. The bug may cause the crystal oscillator to be improperly calibrated. This only applies to Si5518 and SI5512 devices. Plans on those devices that use an external XTAL reference are encouraged to upgrade to 1.4. (COGSFW-4834)

Additional Changes to Existing Features/Functionality

- All si55xx/Si540x/Si536x based devices using firmware 1.4 will require a new patch\_rom file to be applied during the HOST\_LOAD procedure or during an NVM\_BURN. This file will be included in the "Create Boot Files" and "Create Burn Files" export by CBPro. (COGSFW-4487)

- Improved PPS PLL closed loop response and reduced overall lock time in certain cases by improving the initial set frequency algorithm. (COGSFW-4296)

- Improved PPS PLL Holdover Performance. (COGSFW-4606)

- A new field has been added in API REFERENCE\_STATUS called the FCAL\_FAILURE\_FLAG, which indicates an FCAL failure during startup. When an FCAL failure occurs during startup, a GLOBAL\_SOFT\_RESET is triggered. (COGSFW-4533)

- Reformatted the documentation of PLL\_STATUS's STATUS byte to show individual bits to clarify their usage. (COGSFW-4416)

- Split OPNID field in DEVICE\_INFO API command result to allow for future SKY part numbers with a letter in the first OPNID field. For example, SKY61234AB<u>Z</u>1234GM (example only). Users may need to update their OPN ID code to incorporate the new letter field. (COGSFW-4524)

- Improved the API description of HWERR to explain the possible causes. (COGSFW-4534)

- Increased the pad drive strength of I2C outputs. (COGSFW-4569)

## CBPro v4.13.0.3 [ 2024-08-06 ]

Si536x/55xx/540x

- Fixed: in the power estimation window, clicking the Board/Theta-JA popup would crash CBPro (TMGSW-3810)

- Fixed: the *NVM Patching User's Guide* doc link was missing from the project dashboard for some parts (TMGSW-3730)

## CBPro v4.13.0.2 [ 2024-06-10 ]

Miscellaneous

• Improved support for pre-production devices.

# CBPro v4.13.0.1 [ 2024-06-05 ]

### Si536x/55xx/540x

• Fixed: for certain configurations, CBPro could crash if the Pulse Width Select page was selected (TMGSW-3720)

## CBPro v4.13 [ 2024-05-31 ]

### CBPro Release Notes

#### Miscellaneous

- Improved support for pre-production devices.

- Improved the message shown in the OPN wizard when the part/grade/revision is not supported. (TMGSW-3523)

- In the CBPro wizard part/sample list, allow search by package name, such as 8x8 or QFN-56. Package names have been normalized to facilitate this.

- Add "pause" to the end of CLI sample batch files so the window stays open if launched from Windows Explorer. (TMGSW-1140)

#### Si536x/55xx/540x

- Firmware 1.3 is now available and is the new recommended version; see release notes

- Fixed: the EVB GUI Status API tab could hang when using the CBPro field programmer. (TMGSW-3588)

- Fixed: clicking Next> through CBPro wizard very quickly could crash CBPro on the LOL page. (TMGSW-3573)

- Fixed: Si5362/3: in a configuration that required A grade, the design report grade section was using wording inferring other grades were supported even though grade A was forced. (TMGSW-3591)

- Fixed: frequency was removed from PHRD input clock labels in the wizard (TMGSW-3690)

- Fixed: Si5510 did not properly implement O/O static skew. (COGSFW-4198)

- Improved REF OOF alarm thresholds when REFIN=Crystal and OOF\_REF=TCXO/OCXO. (TMGSW-3492)

- Added support for new firmware v1.3 features:

- Input edge interrupts: (TMGSW-3618)

- Configured in new CBPro page, "Input Edge Interrupts."

- The page is hidden by default: enable via Advanced Features page. Note the page is automatically shown if an AccuTime grade is selected.

- INT\_INA/B software interrupt options were added to INTR mask editor. They are enabled by default for new projects, but not for existing projects.

- PPS pulse width select: (TMGSW-3413; COGSFW-3423)

- Configured in new CBPro page, "PPS Pulse Width Select."

- The page is hidden by default: enable via Advanced Features page.

- Available for parts supporting 0.5Hz, 1Hz outputs.

- Multi-group sync: (TMGSW-3636)

- The Si5518/12/10/08 and Si5403/2/1 now support two phase jam groups (0 and 1), which allow independent phase adjustments of two different output groups.

- Configured in new CBPro page, "Sync Groups."

- The page is hidden by default: enable via Advanced Features page.

- Group 0 is selected by default for existing and new projects, but Group 1 can now be selected.

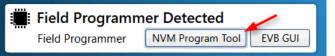

- Added NVM patching support: (TMGSW-3394)

- User configuration (frequency plan) can now be updated in NVM with the field programmer using the NVM Program Tool.

- Uses the latest NVM burn program 1.1 which is embedded in CBPro.

- Host-based NVM patching using the Device API is supported through a new project Export mode in CBPro, whereby a patch file can be generated.

- A user's guide is available for both field programmer and host-based workflows. The guide can be opened from the project dashboard:

and also the NVM Program Tool used with the field programmer:

- The capabilities of Si5512 were expanded: (TMGSW-3600; COGSFW-4205)

- Added support for VCXO mode.

- Changed supported firmware to only v1.3. The user will be warned on opening an older project and it will be switched to v1.3.

- Added support for OSYNC.

- Now support Q output frequencies up to 3.2GHz.

- Device grades were updated.

- Si5508/10: removed references to PPS inputs and improved help text. (TMGSW-3505)

- Improved the DRC error message when Dynamic Phase Adjust is not supported when both Q and R output dividers are required. (TMGSW-3630)

#### Si534x/8x/9x

- Removed OE0/1/2/3\_PIN2DRV registers from export for 1 OE pin parts. (TMGSW-3579)

- Removed BETA label from estimated phase noise plots. (TMGSW-3710)

#### Si5332

- Fixed: an output could be disabled in multi-profile configuration. (TMGSW-3536).

- Fixed: when an output was used in buffer mode, there was no output clock divider setting in CBPro. (TMGSW-2842)

- Fixed: PLL Input (Buffer) was not selectable in CBPro when XA/XB of SI5332 is unused. (TMGSW-3510)

- Improved design report and the OPN datasheet addendum when "Disable I2C Bus" is checked. (TMGSW-2678)

- In multi-profile, display new message in place of I2C Base Address in the NVM text file when I2C is disabled. (TMGSW-3584)

• A DRC error is now generated when there is no selection made for Output Clock Dividers under the Pin Controlled Frequency Select. (TMGSW-3584)

### AccuTime Assistant Release Notes

- Added the ability to view or change verbosity channels for ptpstack in "Log Level Status" panel in right "Status Bar".

- Added new configuration parameters introduced in AccuTime v3.2 and v3.3 to "PTP Config Editor" tab. (TMGSW-2929)

- Added the ability to select AccuTime version which in turn makes unsupported configuration parameters read only by default in the GUI and does not include them in output file in "PTP Config Editor" tab. (TMGSW-2929)

- Added the ability to hide unsupported configuration parameters in "PTP Config Editor" tab as dictated by AccuTime version selection instead of making them read only. (TMGSW-2929)

- Added the ability to cancel download of log files in "Log Tracker" tab.

- Added the ability to do a intermediate SSH hop when connecting to an AccuTime enabled platform while maintaining functionality including download/upload. (TMGSW-3310)

- Add ability to auto set AccuTime Version and PTP Config File based on running DUT. (TMGSW-2929)

- Refactored file download infrastructure to reuse client. This should in theory make it faster to download files instead of having to re-establish connection for every file which was done previously.

- Ensure ifconfig is shown when connected to a device. (TMGSW-3609)

### Si536x/540x/55xx Firmware 1.3 Release Notes

- The Si5512 now includes support for the JESD\_SYSREF\_PULSER API command. (COGSFW-3809)

- Execution of commands with incomplete arguments will now fail with a bad argument error. The command

action is not taken in this case. The following commands are affected: MANUAL\_INPUT\_CLOCK\_SELECT,

VARIABLE\_OFFSET\_DCO, FORCE\_HOLDOVER, PHASE\_JAM\_SYNC\_OUT, and PLL\_SOFT\_RESET. (COGSFW-3864)

- Fixed bug where PHDEC API had a slightly different step value than the assigned step value. All steps in both the PHINC and PHDEC API now match step value exactly. (COGSFW-3832)

- The OUTPUT\_ENABLE API now returns the current enabled status of outputs. (COGSFW-3732)

- Firmware now supports 50% or less duty cycle options for 1 PPS and 1 PP2S outputs. (COGSFW-3653)

- Added new LOSS\_OF\_LOCK\_XO field to REFERENCE\_STATUS API, which informs the user if the XO PLL Loses Lock (COGSFW-3612)

- Added a new DCO\_READOUT API command, which will return the current DCO applied to a divider from VARIABLE\_OFFSET\_DCO. (COGSFW-3449)

- INA and INB input rising edge interrupt source added for low frequency (<10 Hz) inputs. (COGSFW-3690)

- Fixed potential FSC overflow issue which could result in unexpected spurs on output clocks on select frequency plans (COGSFW-4018)

- Fixed issue where polling the PHINC/PHDEC\_IN\_PROGRESS bit when NSTEPS=0 incorrectly returned BADARG instead of reporting the current status. (COGSFW-4251)

#### Si536x/540x/55xx NVM Burn Program v1.1 Release Notes

- NVM\_BURN has several new commands to support patching the user configuration NVM (frequency plan, FPLAN):

- NVM\_FPLAN\_PATCH\_INVALIDATE disable a previously applied user configuration patch in preparation for applying a new patch.

- NVM\_FPLAN\_CRC Report the CRC of the active user configuration and the CRC of the baseline user configuration from which it is derived.

- NVM\_FPLAN\_READ\_INIT Initialize the read of a baseline user configuration stored in NVM.

- NVM\_FPLAN\_READ Read the baseline user configuration stored in NVM.

- NVM\_SPACE\_AVAILABLE.ENTRIES\_AVAILABLE reports the number of file descriptors available for further NVM programming.

- NVM\_BURN\_VERIFY.NUMBYTES now reports the number of bytes programmed, including any ECC bytes.

- NVM Burn command buffer size increased to 32768 bytes.

- Additionally, NVM\_BURN supports more robust burn files which contain embedded file integrity information as well as safety features to ensure a frequency plan patch is being applied to the correct device. CBPro 4.13 and higher generates robust burn files. The burn firmware is backwards compatible, supporting burn files generated by earlier versions of CBPro. Note burn files created by CBPro 4.13 and higher are not supported by NVM burn program v1.0.

## CBPro v4.12.0.3 [ 2024-03-06 ]

Si536x/55xx/540x

• Fixed: there was an error trying to create an Orderable Part Number (OPN) with a "blank" (no firmware) configuration (TMGSW-3571)

## CBPro v4.12.0.2 [ 2024-02-24 ]

### Si536x/55xx/540x

- Fixed: there could be problems reliably communicating with some EVBs (TMGSW-3501)

- Fixed: the NVM Program Tool did not reboot the part correctly after NVM activities, leading to an error when trying to verify that the DUT was in application mode. The APP\_INFO command would fail to execute because of this (the DUT was in bootloader mode instead of application mode). The NVM was still programmed correctly. (TMGSW-3568)

Both issues were only present in CBPro 4.12 and 4.12.0.1.

## CBPro v4.12.0.1 [ 2024-02-16 ]

Si5342/4/5

• Fixed: the XA/XB XTAL option was missing in CBPro 4.12 when creating a new project (TMGSW-3512)

## CBPro v4.12 [ 2024-01-19 ]

Added support for pre-release devices

#### Miscellaneous

- Fixed: reading or writing very large DUT settings in EVB GUI could show different value in GUI than the actual DUT value (TMGSW-3379)

- Fixed: forcing of US-based number formatting and parsing stopped working in CBPro 4.10 with the change to .NET4.8, causing CBPro errors with certain parts on locales that use "," as the decimal separator, such as France (TMGSW-3443)

- Fixed: on the Field programmer, changing the serial interface mode did not always result in successful DUT scan/reads, requiring CBPro restart (TMGSW-2580)

Si536x/55xx/540x

- Fixed: after writing a project, CBPro could report "Error running design checker: object reference not set an instance of an object" as a sole DRC error (TMGSW-3313)

- Fixed: the OOF Reference editor and design report listed XAXB even if XO selected as reference (config was OK, reporting issue) (TMGSW-3349)

- Fixed: Si5360: selecting XTAL\_XO divider was causing a DRC error

- Fixed: the common mode voltage of the clocks was being set too low when using custom differential modes of 500 and 600. Previously it was being set to 0.9V. Now it is being set to 1.2V unless the VDD voltage is 1.8V (COGSFW-3764)

- Fixed: VCXO buffered outputs were causing invalid DRC error + exception on output page

- Improved PLL bandwidth ratio 10x ratio DRC warning text

- If device grade is changed to AccuTime on the Device Revision page, the "Force DSPLL A into free run on device startup and reset" option on Input Clock Selection will be changed to checked; likewise, if you change to non-AT, it will be unchecked. Existing project files will never be changed unless you switch between AT and non-AT. Updated Si540x, Si5518 APTS, and Qualcomm small cell reference design sample project files with this new default. (TMGSW-3030)

- Added support to create OPNs with firmware but no configuration, to speed up customer in-system programming workflows (TMGSW-3077)

- OOF improvements (TMGSW-3456)

- Fixed: clear threshold was not programmed correctly

- Added "actual" programmed thresholds to the design report

- In wizard, mini OOF report is now available:

| (Set) (Cear) (Set) (Set) (Set) (Set) (Set)                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configured OOF threshold values will be padded with some<br>noise margin to allow reliable OOF operation even under jittery<br>input clock conditions. The actual OOF values with margin<br>included are reported in the design report or by clicking the<br>'OOF Report' button below. |

| OOF Report                                                                                                                                                                                                                                                                              |

- Removed the XO disclaimer on XAXB pages (TMGSW-1537)

- Improved DUT revision check on project write

- Changed HCSL fout(max) from 400M to 500MHz (TMGSW-3420)

- Added support for frequency planner options -- select lowest jitter output or factory selected specific plan -- in the CBProFOTF3 tool (TMGSW-3411)

- Added support for Frequency Planner Options on Si536x (TMGSW-3359)

- Improved DSPLL Startup Behavior tooltip (TMGSW-3404)

- Updated the I2C Host API command driver used with the field programmer to always write API0(0xF0), API1(0x0F) word between API command execution and REPLY check; this ensures no issues when executing RESTART/ GLOBAL\_SOFT\_RESET commands, where the API interface is reset

- Host API documentation and CBPro EVB GUI Device API tab

- Added note to METADATA API description that CBPro does not support the OFFSET field. (COGSFW-3971)

- Clarified the descriptions of "Application" in the APP\_INFO API to make it clear that application refers to the firmware version and the "Firmware" field indicates which firmware is running (i.e. non-PPS, PPS, NVM\_BURN) (COGSFW-3960)

- Updated the GET\_TEMPERATURE\_READOUT example to show both a positive and negative case (COGSFW-3773)

Si5391/2/4/5 E/P Precision Calibration Grades (TMGSW-3319)

- Allow HCSL and LVCMOS (complementary) on any output; a DRC warning will be asserted for each output, and Skyworks highly recommends submitting a Phase Noise Report request for this configuration

- If an LVCMOS and Differential output does not have at least 2 output and corner separation, a DRC error is asserted

- Outputs adjacent to an HCSL output will only support Standard performance

### Si538x

• Fixed: CBPro allowed crystal selection on 5386/82/81 (TMGSW-1881)

#### Si5388/9

• When settings, registers, or regmap is exported, warn about pseudo read-only registers that are included (TMGSW-3154)

#### Si5332

- Fixed: CBPro export + addendum included information about I2C even when disabled (TMGSW-2678)

- Remove LVDS 1.8V option (TMGSW-2825)

- Improve titlebar and sub-title labeling regarding package selection (TMGSW-2814)

#### Si5338

• Fixed: I2C address was not correct in CSV register export; replaced Pre/Post download message with message describing address 27d (TMGSW-1547)

#### Si535x

- Fixed: the input termination description was not correct (TMGSW-1353)

- Fixed: writing an Si5351 settings file generated by CBPro would raise error (TMGSW-3326)

- Added in-phase option to Si5356 output driver setting (TMGSW-2126)

#### Si5335x

• Added Si53350 to updated input termination description (TMGSW-1353)

#### AccuTime Assistant

- Added option to use SCP instead of SFTP for file transfer (TMGSW-3309)

- Added ability hide and dock right "Status Bar" and bottom "miniTerminal"

- Added the ability to remember the hide/dock status of "Status Bar" and "miniTerminal"

- Add "Log Level Status" panel in right "Status Bar" capable to view or change log levels of running applications

- Added "Active Configuration File" to ESMC and PTP Stack in connect tab

- Fix issue in "Save Debug Information ..." button related to dmesg log file

- Changed the behavior of the "Start" button in "Log Tracker" tab to delete the Data and clear the plot (TMGSW-3043)

- Added "Clear Data" button for "Log Tracker" tab that completely deletes the data and also clears the plot to allow for more control of the realtime plotting capability

- Added ability to see which file is being download in "Log Tracker" tab after clicking on "Download Log Files" button (TMGSW-3049)

- Add groups for the "Select Plot Parameter" in "Log Tracker" and "PTP Log Parser" tabs

- Enhanced Statistics of "Loopcontrol Messages" section in "Log Tracker" and "PTP Log Parser" tabs by ensuring Parameter name stays visible and allowing the statistics to be collapsed/expanded

- Added the ability to remember the collapse/expand status of the statistics inside "Loopcontrol Messages" section in "Log Tracker" and "PTP Log Parser" tabs

- Added the infrastructure to add more information about loopcontrol events

- Fixed missing statistics for "ptp2config st i" in "PTP2Info" tab (TMGSW-3399)

## CBPro v4.11.0.1 [ 2023-09-14 ]

#### Si534x/9x

• Fixed: projects converted from 10- to 12-output parts (Si5341 -> Si5391, Si5345 -> Si5395, Si5346 -> Si5396) with CBPro 4.11 could not export programming data or create OPNs. There is no need to re-convert any existing projects, as this version of CBPro will "fix" any projects converted with 4.11. (TMGSW-3351)

## CBPro v4.11 [ 2023-08-21 ]

Added support for Si5360 18-Output, Any-Frequency, Any-Output Clock Generator with Ultra-Low Jitter

## CBPro v4.10 [ 2023-07-31 ]

### CBPro Release Notes

#### Miscellaneous

- Moved to .NET Framework 4.8

- With this change, Windows Vista support is dropped

#### Si536x/540x/55xx

- Firmware 1.2 is now available and is the new recommended version; see <u>release notes</u>

- Fixed: PPS PLL could not be locked in certain configurations (TMGSW-2871; COGSFW-3152)

- Fixed: the CBProFOTF3 FOTF CLI tool did not stop when no common VCO frequency could be found

- Fixed: in Automatic switching mode and if all clocks are set to non-revertive mode, the part remains in revertive mode (TMGSW-3085)

- Fixed: 0.5Hz, 1Hz inputs could be assigned to other PLLs if they were also assigned to PPS\_PLL (TMGSW-3071)

- Expanded number of possible frequency planner solutions, allowing more configurations to be generated without error and optimizing phase noise performance (COGSFW-2987)

- Removed CLEAR\_STATUS\_FLAGS text in Interrupt Configuration page, describing recommended INTERRUPT\_STATUS clear behavior in its place (TMGSW-3143)

- Si5361/2/3: updated the default bandwidth ranges: DSPLLP: 20 400 Hz DSPLLA/B: 20 4000 Hz (TMGSW-3148)

- Improved Input Switching label on PPS PLL page (TMGSW-3101)

- Added Qualcomm Small Cell Reference sample project files (TMGSW-3042)

- Removed DRC error if PLLA has PHRD\_FB output with PTP Steered-RF (TMGSW-3185)

- Allow secondary SPI checkbox to be selected by anyone (TMGSW-3106)

#### Si534x/7x/8x/9x

• Fixed: could not create an Si5386 Orderable part Number (OPN) ()

- Fixed: Si5340/41/9: LOS thresholds and val time were not editable (TMGSW-3108)

- In DCO report, if N=7.5 explain differences between effective Nx divider value to be used in DCO calculations vs. DUT register value (TMGSW-3062)

- Report device revision instead of Skyworks internal die revision in customer export headers (TMGSW-2279)

- Support OE pin configuration on devices with 2 or more OE pins: Si5346/47/48/96/97 (TMGSW-2850)

#### Si5338/35

- Fix C Code register export: register 230 is not included, with 0x0F mask (TMGSW-3197)

- Add HSTL/SSTL complementary & in-phase output driver options (TMGSW-2603)

#### Si5332

- Fixed: When using the Si5332 in buffer mode (NO PLL input, CLKIN2 and CLKIN3 are selected as "buffer"), CBPro gives an error saying "profile not sufficiently complete to calculate frequency plan" (TMGSW-3110)

- Fixed: CBPro power estimate was missing buffered outputs (TMGSW-3194)

#### AccuTime Assistant

- Fix firmware version parsing exception and ATA compatibility warning (TMGSW-3198)

- Fix ifconfig showing inaccurate information after load script (TMGSW-3224)

### Si536x/540x/55xx Firmware 1.2 Release Notes

#### Bug fixes and Improvements

COGSFW-3450 5500: PLL\_LOOP\_FILTER\_RAMP\_IN\_PROGRESS API reply does not assert when in frequency slop limiting (FSL) or phase slope limiting (PSL)

API function modified to include FSL and PSL along with hold over exit ramp when reporting RAMP\_IN\_PROGRESS.

COGSFW-3225 PPS PLL auto-relock phase limit should apply to the total phase instead of the phase with bleedout subtracted

Fixed PPS\_PLL auto relock threshold issue which could cause auto relock to not occur in certain scenarios such as exiting holdover.

- COGSFW-2894 PPS PLL does not lock with the NA divider output as ZDM feedback Fixed PPS PLL initial lock issues when PPS ZDM is sourced from NA divider.

- COGSFW-3593 GPIO state logic bug Would impact startup when GPI forced holdover mode is used The forced holdover via pin feature had a bug that if the feature were enabled, the pin would always readback as "force holdover". This causes the device to skip waiting for those PLLs to lock. If a set lock order is desired, this could cause issues. The bug is now fixed, and the pin will be interpreted correctly.

- COGSFW-3176 Put PPS\_PLL into free run when RFPLL/REF\_PLL/PLLP goes unlocked PPS PLL will enter free run when PLLR enters holdover or short-term holdover.

- COGSFW-3226 PPS PLL coarse+fine LOL claims to be locked during PPI even with large phase offset. Fixed PPS\_PLL LOL behavior when exiting holdover.

- COGSFW-3363 PPS PLL: Improved handling of freerun vs holdover

- COGSFW-3432 JESD 204B Pulse mode busy, not pulsed Fixed SYSREF Pulser always busy in some configurations where continuous SYSREF is included.

- COGSFW-3284 Improved jitter optimization for the Si536x.

#### API Documentation Improvements

- COGSFW-2354/COGSFW-3036 DEVICE\_INFO is missing a pad byte

- COGSFW-3044 DEVICE\_INFO links are wrong Corrected the HTML links for DEVICE\_INFO API command.

- COGSFW-3237 Add notice to top of Device API HTML documentation documenting location of firmware release notes

Updated the API HTML to point to CBPro for release notes.

COGSFW-3516 Add "or FWERR" to READ\_REPLY Minor adjustment to READ\_REPLY API command description to account for FW\_ERR.

# CBPro v4.9 [ 2023-04-11 ]

Si536x/540x/55xx

- Fixed: I/O alignment could be out of specification if a configuration used Q or NB divider but NA divider was not used; this only occurred in CBPro 4.7.6 through 4.8.6 (COGSFW-3370)

- Fixed: the DRC warning for differences between GPIO digital logic voltages could be triggered erroneously and report "NaN" VDDIO voltage (TMGSW-3031)

- Adjusted bandwidth ranges, defaults and PLL interaction DRC BW ratio checks and synchronized sample projects to the defaults (TMGSW-2982; TMGSW-3035; TMGSW-3041)

New recommended, default bandwidths:

| Part / Topology                            | PLLP/RFPLL/REF_PLL | PLLA   | PLLB   |

|--------------------------------------------|--------------------|--------|--------|

| Si536x, Si55xx Single Ref                  | 30 Hz              | 300 Hz | 300 Hz |

| Si55xx Dual Ref CG, Si540x PLLA disabled   | 30 Hz              | 300 Hz | 300 Hz |

| Si5512/18 Dual Ref JA, Si540x PLLA enabled | 30 Hz              | 2 Hz   | 300 Hz |

| Si5512/18 Dual Ref JA PTP Steered-RF       | 30 Hz              | 2 Hz   | 2 Hz   |

- Added support for the CBProProjectEdit CLI, which supports editing input/output MUX and frequencies via small text files, creating new project file as an output. This plus existing CBProBootfileExport CLI can be used to create larger edits for full reconfiguration scenario, complementing FOTF. See the <u>CBProProjectEdit user manual</u> for examples and <u>CBPro Tools & Support for In-System Programming</u> for an overview of in-system programming options. (TMGSW-3022)

- Estimated power improvements: improve calculation accuracy + updated Theta-JA no airflow values to match datasheet (TMGSW-3013)

- Removed unsupported "Unassigned" option on API input select combo (TMGSW-3025)

- Improved free-run page warning for Si5362/3 (TMGSW-3011)

#### Si540x/55xx Only

- It is now a DRC error to have an input MUXd to both RFPLL/REF\_PLL and PLLA on Si540x or Si5512/18 Dual-Reference JA (TMGSW-2960)

- OCXO/TCXO and OOF Reference changes (TMGSW-2960)

- o Si5512/18

- Only max 2 TCXO/OCXO references can be defined; it is now a DRC error if 3+ are selected

- Holdover reference type must now be selected for PLLR inputs; a DRC error "INx: holder reference type must be defined" may be seen on existing project files that violate this rule

- Due to this change, the minimum input frequency for a PLLR input is 10MHz

- On OOF page, if there are 2 OCXO/TCXO references only XAXB can be selected as OOF Reference

- o Si540x

- OCXO/TCXO reference is now defined on the input clocks page

- Up to 2 clocks (REF and/or INx) can now be assigned to REF PLL and be an OCXO/TCXO reference

- OOF reference logic has been adjusted:

- There is now a "set for me" checkbox and this is checked by default

- If there is only a single OCXO/TCXO reference, it will be the default

- If there are 2 OCXO/TCXO references, OCXO/TCXO cannot be selected and XAXB will always be used

- Added DRC warning if OOF reference is not OCXO/TCXO (TMGSW-2960)

- Changed RFPLL/REF\_PLL max bandwidth from 4k to 400 Hz (TMGSW-3041)

- Bandwidth/Fpfd ratio check is now performed on desired BW, not estimated actual (TMGSW-2982 ; TMGSW-1813)

#### Si540x Only

- The MA DCO option is no longer supported on new projects when the PPS PLL is disabled (TMGSW-2965)

- Added Qualcomm Small Cell grade E option to the Device Revision & Grade page (TMGSW-3044)

#### Si51211/18

Added DRC warning that these parts are <u>not recommended for new design</u> and OPN is not supported (TMGSW-3065)

#### Si5332/57

• Fixed: invalid pin mux settings could be included in an OPN if Frequency Select was swapped between O/N dividers (or vice versa) (TMGSW-2605)

#### Si534x/7x/8x/9x

• Force field programmer firmware v0.83 to fix issues with 1.8V SPI (TMGSW-2972)

#### Si535x

• Fixed: CBPro crashed if phase offset was blank (TMGSW-2769)

#### M64/M68/M88 Modules

• Fixed: CBPro reported "Error running design checker" (TMGSW-3057)

#### AccuTime<sup>™</sup> Assistant (password required; contact Skyworks for access)

- A new User Guide is available in the tool; available from the Host Connection panel (TMGSW-3019)

- Added automatic detection of Host disconnect (TMGSW-3034)

- Added the ability to run/load setup scripts on Xilinx-based demo platforms (TMGSW-2783)

- Added the ability to run the Skyworks Sample ESMC Stack (TMGSW-2838)

- Added ESMC Stack status indicator to the status bar (TMGSW-2838)

- Added PTP2 Info tab that displays the PTP stack information available through ptp2config (TMGSW-2539)

- Added automatic polling of indicators and information throughout the tool (TMGSW-2606)

- Many commands are now run on a secondary background shell while the primary shell is used for mirroring the log, ensuring the user interface is responsive and more up-to-date (TMGSW-2606).

- Added tooltips for all plotting options (TMGSW-3033)

- Added a checkbox ("Use All Data and Events") to the Log Tracker and PTP Log Parser that displays the events that happened outside the plot limits

# CBPro v4.8 [ 2023-02-14 ]

#### Si536x/Si540x/Si55xx

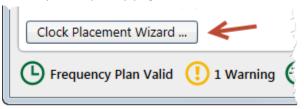

- Fixed: if clock placement wizard was used, OUT6/11 GPIOs could be mislabeled in the wizard (TMGSW-2968)

- Fixed: clock placement wizard could crash when a GPI output was present (TMGSW-2949)

- Fixed: it was possible to get a "parameter name index" DRC error for projects changed from single to dual reference (TMGSW-2958)

- Fixed: on Si55xx with PTP Steered-RF, could receive error 'No legal values for PB ratio after DRC check' when TCXO/OCXO used would result in fractional Px input divider (TIMINGSYS-1164)

- Fixed: clicking Next> on the Outputs page could show error popup about unassigned divider even though not applicable (TMGSW-2984)

- Fixed: after writing a project file, logging in the EVB GUI could be disabled (TMGSW-2990)

- Si540x:

- Fixed: the topology diagram could be stuck in a cleared state (TMGSW-2942)

- Add support for NA cascaded from DSPLLB; selected on Topology page (TMGSW-2896)

- Si5361/2/3

- Fixed: if there was a ZDM input and all non-ZDM outputs were "Auto" divider, received DRC error "you must assign a non-Zero Delay Mode output to DSPLL P" (TMGSW-2924)

- Custom Orderable Part Numbers (OPN) can now be created by any customer (TMGSW-2981)

- Improve output divider 'Auto' algorithm (COGSWORTH\_FW-3149)

- Allow ZDM output divider to be Auto; if a ZDM input is added, set the auto created ZDM output to Auto instead of forcing on Q (TMGSW-2924; TMGSW-2941)

- Si5512/18: change Synchronization Modes NB output tracking option default from PTP to OCXO/TCXO; sample projects also updated (TMGSW-2927)

- Add "GPS Input" checkbox to PHMON page; when checked, auto set threshold is set to 25 ns (TMGSW-2914)

- Allow adjustment of estimated power core supply voltage assumptions (TMGSW-2971)

- Coupling DRC message improvements (TMGSW-2936)

#### Si534x/7x/8x/9x

- Fixed: changing an output to custom differential could cause error "unexpected Si538xVoltageSwingMode" (TMGSW-1116)

- Fixed: with a Si5391/5 project, when writing to EVB the OUT0A driver format was not configured properly (TMGSW-2964)

- Fixed: the EVB GUI "All Voltages" tab had unreadable layout (TMGSW-2987)

#### Si5332, Si5357

- Fixed: airflow was not selectable in the power estimation window when embedded XTAL was selected (TMGSW-2935)

- Support burning NVM when target DUT has I2C\_A0 asserted, and current device I2C address is different than the "base" I2C address to be programmed (TMGSW-2969)

#### Miscellaneous

- Fixed: opening a project file shows "Step 1 of X" in header instead of Dashboard label (TMGSW-2986)

- New EVB GUI DUT Settings Dump tool

- Can be used to read and save all device settings on Si534x/7x/8x/9x, Si5332, Si5357

- This returns the same data that CBProDeviceRead --all command line tool does

#### • Example:

| nfo DUT Settings Editor DUT Register Editor DUT Settings Dump Status |                |           |         |                |                     |          |             |            |  |

|----------------------------------------------------------------------|----------------|-----------|---------|----------------|---------------------|----------|-------------|------------|--|

| Re                                                                   | efresh Setting | IS        | Save to | CSV            |                     |          |             |            |  |

| <b>-</b>                                                             |                | al (satti |         | e matching Ol  | D and CAL): 1000 (  | ottinge  | at register | = 0×1000)  |  |

| EXc                                                                  | amples: old ca | ai (setti | ng name | es matching Of | D and CAL); 1000 (؛ | settings | at register | r 0x 1000) |  |

|                                                                      | Location       | NVM       | Туре    | Name           |                     | Value    | Value       |            |  |

|                                                                      | 0x0000[3:0]    | None      | R/O     | DIE_REV        |                     | 6        | 0x6         |            |  |

| ľ                                                                    | 0x0002[15:0]   | SiLab     | R/W(L)  | PN_BASE        |                     | 21396    | 0x5394      |            |  |

| ľ                                                                    | 0x0004[7:0]    | User      | R/W     | GRADE          |                     | 10       | 0xA         |            |  |

| L                                                                    | 0x0005[7:0]    | SiLab     | R/W(L)  | DEVICE_REV     |                     | 0        | 0x0         |            |  |

| ľ                                                                    | 0x0006[23:0]   | User      | R/W     | TOOL_VERSIO    | N                   | 525327   | 0x8040F     |            |  |

| ľ                                                                    | 0x0009[7:0]    | SiLab     | R/W(L)  | TEMP_GRADE     |                     | 0        | 0x0         |            |  |

| Ľ                                                                    | 0x000A[7:0]    | SiLab     | R/W(L)  | PKG_ID         |                     | 5        | 0x5         |            |  |

| Ľ                                                                    | 0x000B[6:0]    | SiLab     | R/W     | I2C_ADDR       |                     | 104      | 0x68        |            |  |

|                                                                      | 0x000C[0]      | None      | R/O     | SYSINCAL       |                     | 1        | 0x1         |            |  |

|                                                                      | 0x000C[1]      | None      | R/O     | LOSXAXB        |                     | 0        | 0x0         |            |  |

|                                                                      | 0x000C[5]      | None      | R/O     | SMBUS_TIMEC    | UT                  | 0        | 0x0         |            |  |

|                                                                      | 0x000D[3:0]    | None      | R/O     | LOS            |                     | 0        | 0x0         |            |  |

|                                                                      | 0000017.41     | News      | D/O     | 005            |                     |          | 00          |            |  |

## CBPro v4.7 [ 2022-11-18 ]

Added support for Si5361/2/3 18-Output, Any-Frequency, Any-Output Jitter Attenuator/Clock Multiplier with Ultra-Low Jitter

Miscellaneous

- Work around Acrobat error when CBPro tried to open a PDF (TMGSW-2492)

- CBPro release notes and documentation can now be opened from the "Design Dashboard" in addition to CBPro welcome screen

• Add AccuTime Assistant shortcut option to CBPro installer (TMGSW-2891)

#### Si534x/7x/8x/9x

- Fixed: CBProFOTF1 CLI could raise "object reference" error if a clock expression referenced another clock (TMGSW-2886)

- In power estimate, add breakout by regulator voltage

- EVB GUI estimated power comparison to actual now uses measured regulator voltage when calculating estimated power instead of requested (TMGSW-2285)

#### Si536x/Si540x/Si55xx

- Estimated power and device junction temperature (Tj) is now reported (TMGSW-2285; TMGSW-2875)

- Click the power widget in CBPro to view a breakdown of power estimate by regulator and change estimate assumptions, such as ambient temperature (Ta), board/O<sub>JA</sub>, and core supply regulator voltages.

Frequency Plan Valid 🕢 Design OK 😯 Typical Pd 2.04 W, Tj 46 °C

• Also included in design report

- The model is preliminary. Use the EVB GUI Regulators comparison tool and Device API TEMPERATURE\_READOUT command to measure actual current and Tj under typical and worst-case operating conditions.

- Firmware 1.1 only (Si5361/2/3 always firmware 1.1; Si540x/Si55xx where selected)

- Coupling (crosstalk) improvements (TMGSW-2864)

- LVCMOS clocks no longer generate DRCs as victim (TMGSW-2864)

- A new model is used to evaluate potential coupling between outputs based on estimated spurs and resulting jitter. Spurs and jitter for outputs with up to 4 gaps between each clock is estimated.

- Critical coupling issues are now identified by ① on the output page, while less critical referred to as significant coupling is identified by ①. The design report and indicator tooltip explain the thresholds used in scoring.

- Detailed spur and jitter data available in design report and from new "Spur Analysis" button on the Outputs page:

Spur Analysis ... Clock

Clock Placement Tool ...

- FOTF improvements

- Fixed: FOTF CLI would throw error generating template files when an LOS offset was not editable (TMGSW-2876)

- Fixed: could get "Value was either too large or too small for an Int64" when running tool (TMGSW-2878)

- Add check for firmware 1.0 selection, aborting if in project file (TMGSW-2877)

- New CBProBootfileExport command line tool (TMGSW-2885)

- Exports volatile in-system programming files

- Given a project file, saves user\_config.boot.\*, prod\_fw\*.boot.\*, and design\_report.txt

- o Complete user manual via CBProBootfileExport –help or the <u>CLI User's Guide</u>

- Also added to <u>CBPro Tools & Support for In-System Programming</u> training

- Remove I2C warning when an AccuTime grade is selected; AccuTime now supports fully supports either I2C or SPI (TMGSW-2892)

- Si540x: added support for PPS PLL modulating NA divider (TMGSW-2881)

- Si540x: in OOF and PHMON, hide REF in GUI and design reports as these are don't cares (TMGSW-2790)

- Fixed Synchronization mode text (TMGSW-2872)

- Fixed Xilinx Ultrascale typo (TMGSW-2867)

- Fixed: if PPS PLL was previously enabled and an input clock was assigned to it and later PPS PLL was disabled, CBPro might still think an input was assigned to this PLL (TMGSW-2848)

- Improved performance of the EVB GUI Status API tab, especially when multiple EVBs are attached and GUIs open (TMGSW-2851)

- Hide firmware version selection, low power mode enable when custom blank part mode is enabled, since these are not applicable (TMGSW-2786)

# CBPro v4.6 [ 2022-10-07 ]

### Si5512/18 PTP-Steered RF + SyncE Mode

This is a mode to support applications which use PTP alongside Synchronous Ethernet (SyncE) in which the NetSync device must operate as a G.8262/G.8262.1-compliant SyncE wander filter while simultaneously providing low phase noise/low jitter PTP-steered output clocks. A typical example of such a use case would be a 5G radio device that requires PTP-steered low noise clocks for driving the RF data converters and which includes a down-stream, SyncE-capable, data port to allow daisy-chaining of additional radio units.